Сегодня сказали, что метеоритом там и не пахнет....Упавший в Хабаровском крае метеорит снёс вершину сопки, скала обрушилась и перекрыла русло реки Бурея. Как рассказал ИА «Хабаровский край сегодня» глава Верхнебуреинского района Алексей Маслов, происшествие случилось несколько дней назад, но из-за безлюдности мест его не удалось обнаружить сразу.

- Судя по всему, метеорит был громадный, если он смог засыпать русло реки на 40 метров, сейчас к месту выдвинулись две группы, одна из Верхнебуреинского района, другая из Амурской области, - говорит Алексей Маслов. – У них есть спутниковый телефон и дозиметры для определения уровня радиации. На Бурейской ГЭС несколько дней отмечали, что снизился приток в водохранилище, но не могли определить причины. Надеюсь, скоро группы доберутся до места и выяснят подробности. По предварительным данным, русло Буреи засыпано в нескольких километрах выше от устья реки Тырма, примерно в 70 км от посёлка Чекунда. О происшествии сообщено министру МЧС, к оценке обстановки привлечены космические спутники.

Вы используете устаревший браузер. Этот и другие сайты могут отображаться в нем неправильно.

Необходимо обновить браузер или попробовать использовать другой.

Необходимо обновить браузер или попробовать использовать другой.

Высокоученые новости

- Автор темы b-graf

- Дата начала

Ну да, от метеорита будет грохот и яркие световые эффекты.Сегодня сказали, что метеоритом там и не пахнет....

Я года четыре назад тоже след метеорита искал на окрестной сопке. Смотрю, деревья поваленные лежат, гарью воняет, а вокруг снег лежит - не иначе метеорит. Примерно второго января было. Ползал, ползал... Оказалось таки лесной пожар. Но сверху выпал снег и следы пожара почти исчезли).

Diletant

Великий Магистр

Полагаете, остатки продырявленного ими Союза? Или вернувшиеся обломки Фобос-Грунта?Я вот думаю, не происки ли это натофашистов?типа наверное хотели вывести из строя Бурейскую ГЭС.

Знамение, покайтесь грешники:

https://www.bbc.com/russian/features-46944443

В ночь на понедельник, 21 января, жители северного полушария могли наблюдать довольно редкое сочетание трех астрономических явлений, которое называют кровавой волчьей суперлуной.

https://www.bbc.com/russian/features-46944443

b-graf

Принцепс сената

Про РАН или жЫр сгущается...

https://scinquisitor.livejournal.com/165934.html#cutid1

https://scinquisitor.livejournal.com/165934.html#cutid1

b-graf

Принцепс сената

Веривший в теорию плоской Земли инженер погиб при запуске ракеты в США

https://ria.ru/20200223/1565112272.html?utm...andex.ru%2Fnews

https://ria.ru/20200223/1565112272.html?utm...andex.ru%2Fnews

Что поделать, это судьба многих первопроходцев:

https://ria.ru/20200223/1565112272.html?utm...andex.ru%2Fnews

Известный инженер-любитель, летавший на самодельных ракетах, Майк Хьюс, по прозвищу Безумный Майк, погиб во время одного из своих экспериментов в субботу в США, сообщает издание Los Angeles Times со ссылкой на его агента.

https://ria.ru/20200223/1565112272.html?utm...andex.ru%2Fnews

b-graf

Принцепс сената

Подробности о розыгрыше насчет статьи об угрозе изнасилования собак женского пола на собачьих площадках и др.

https://inosmi.ru/science/20200307/246995465.html

https://inosmi.ru/science/20200307/246995465.html

Всего то и требовалось доказать:

Они признают, что их статьи «бредовые», но не больше других, опубликованных всерьез.

Daniel Kopylow

Перегрин

ECLinPS-Plus в настоящее время является самым быстрым логическим семейством в мире. За время, которое требуется свету, чтобы пройти 1,7 дюйма, устройство ECLinPS-Plus завершает задержку распространения (также

известную как задержка затвора). Новое семейство оснащено триггером с частотой переключения более 3

ГГц, а также задержкой распространения и временем нарастания и спада всего 100 пс.

По своей конструкции технология Bi-Polar ECL демонстрирует более высокое рассеивание мощности по сравнению с CMOS-устройствами. Хотя производительность CMOS продолжает улучшаться, мощность

рассеяния начинает становиться главной проблемой, поскольку рабочие частоты увеличиваются.

Технология CMOS работает по формуле рассеивания мощности, которая приводит к значительному

увеличению рассеиваемой мощности с каждым линейным увеличением частоты. По словам Шокмана, большая разница между технологиями ECL и CMOS заключается в том, что при изменении частоты в уравнении рассеивания мощности ECL ток остаётся неизменным. Так что нет масштабирования частоты независимо от скорости устройства. Напротив, как только частота КМОП повышается, так же растёт и рассеиваемая мощность, что увеличивает вероятность

отказа устройства из-за перегрева. По мере увеличения частоты работы устройства CMOS возникает момент, когда и CMOS и ECL будут потреблять одинаковое количество энергии. Выше этой точки пересечения,

устройства ECL поддерживают относительно постоянное рассеивание мощности и, следовательно, высокую надёжность на более высоких частотах. На частотах выше точки пересечения, CMOS-устройства будут сталкиваться с растущими требованиями рассеивания мощности. «Точка пересечения может отличаться

от устройства к устройству (ECL против CMOS), но её можно рассчитать для конкретных случаев.

Как правило, - отмечает Шокман, - вам, вероятно, будет безопасно разместить точку пересечения

примерно на 500 МГц.»

ECL всегда считалась очень мощной. Однако современная субмикронная геометрия привела к тому, что рабочее напряжение ECL снизилось до 2,5 В, а утечка тока снизилась до минимума или ниже, чем у CMOS. Это правда, хотя CMOS работает на одну пятую скорости. Однако технология не может конкурировать ни по скорости, ни по мощности с субмикронным ECL. ECL имеет меньшую мощность во многих приложениях и будет работать в пять-десять раз быстрее.

Сравнение между CMOS и ECL также дало интересные результаты. Для некоторых наиболее важных транзакционно-ориентированных рабочих нагрузок система CMOS с восемью (более медленными) процессорами обеспечивала почти такой же отклик, что и система ECL с шестью (более быстрыми) процессорами. Де Сантис отметил, что это отчасти связано с тем, что удлинение времени обработки для системы CMOS уравновешивается уменьшением задержки в очереди из-за доступности двух дополнительных процессоров CMOS. Тот факт, что эти рабочие нагрузки требуют интенсивного ввода-вывода, а не процессора, также является важным фактором.

С другой стороны, время отклика в системе CMOS было на 37% больше для более низкоприоритетных, более загруженных процессором пакетных рабочих нагрузок.

Время распространения для этой компоновки может быть меньше наносекунды, включая задержку сигнала на вход и выход из пакета IC. Какой-то тип ECL всегда был самым быстрым логическим семейством.

Из-за дифференциально-усилительного характера ECL ток затвора остаётся приблизительно

постоянным и просто направляется от одной стороны затвора к другой в зависимости от входных

логических сигналов. Таким образом, ток питания и, следовательно, рассеяние мощности затвора

ECL остаются относительно постоянными независимо от логического состояния затвора.

ECL имеет наивысшее рассеивание мощности, предъявляя штраф за лучшую производительность. Рассеиваемая мощность CMOS и TTL увеличивается с частотой работы. Рассеиваемая мощность ECL остаётся постоянной, независимо от рабочей частоты.

известную как задержка затвора). Новое семейство оснащено триггером с частотой переключения более 3

ГГц, а также задержкой распространения и временем нарастания и спада всего 100 пс.

По своей конструкции технология Bi-Polar ECL демонстрирует более высокое рассеивание мощности по сравнению с CMOS-устройствами. Хотя производительность CMOS продолжает улучшаться, мощность

рассеяния начинает становиться главной проблемой, поскольку рабочие частоты увеличиваются.

Технология CMOS работает по формуле рассеивания мощности, которая приводит к значительному

увеличению рассеиваемой мощности с каждым линейным увеличением частоты. По словам Шокмана, большая разница между технологиями ECL и CMOS заключается в том, что при изменении частоты в уравнении рассеивания мощности ECL ток остаётся неизменным. Так что нет масштабирования частоты независимо от скорости устройства. Напротив, как только частота КМОП повышается, так же растёт и рассеиваемая мощность, что увеличивает вероятность

отказа устройства из-за перегрева. По мере увеличения частоты работы устройства CMOS возникает момент, когда и CMOS и ECL будут потреблять одинаковое количество энергии. Выше этой точки пересечения,

устройства ECL поддерживают относительно постоянное рассеивание мощности и, следовательно, высокую надёжность на более высоких частотах. На частотах выше точки пересечения, CMOS-устройства будут сталкиваться с растущими требованиями рассеивания мощности. «Точка пересечения может отличаться

от устройства к устройству (ECL против CMOS), но её можно рассчитать для конкретных случаев.

Как правило, - отмечает Шокман, - вам, вероятно, будет безопасно разместить точку пересечения

примерно на 500 МГц.»

ECL всегда считалась очень мощной. Однако современная субмикронная геометрия привела к тому, что рабочее напряжение ECL снизилось до 2,5 В, а утечка тока снизилась до минимума или ниже, чем у CMOS. Это правда, хотя CMOS работает на одну пятую скорости. Однако технология не может конкурировать ни по скорости, ни по мощности с субмикронным ECL. ECL имеет меньшую мощность во многих приложениях и будет работать в пять-десять раз быстрее.

Сравнение между CMOS и ECL также дало интересные результаты. Для некоторых наиболее важных транзакционно-ориентированных рабочих нагрузок система CMOS с восемью (более медленными) процессорами обеспечивала почти такой же отклик, что и система ECL с шестью (более быстрыми) процессорами. Де Сантис отметил, что это отчасти связано с тем, что удлинение времени обработки для системы CMOS уравновешивается уменьшением задержки в очереди из-за доступности двух дополнительных процессоров CMOS. Тот факт, что эти рабочие нагрузки требуют интенсивного ввода-вывода, а не процессора, также является важным фактором.

С другой стороны, время отклика в системе CMOS было на 37% больше для более низкоприоритетных, более загруженных процессором пакетных рабочих нагрузок.

Время распространения для этой компоновки может быть меньше наносекунды, включая задержку сигнала на вход и выход из пакета IC. Какой-то тип ECL всегда был самым быстрым логическим семейством.

Из-за дифференциально-усилительного характера ECL ток затвора остаётся приблизительно

постоянным и просто направляется от одной стороны затвора к другой в зависимости от входных

логических сигналов. Таким образом, ток питания и, следовательно, рассеяние мощности затвора

ECL остаются относительно постоянными независимо от логического состояния затвора.

ECL имеет наивысшее рассеивание мощности, предъявляя штраф за лучшую производительность. Рассеиваемая мощность CMOS и TTL увеличивается с частотой работы. Рассеиваемая мощность ECL остаётся постоянной, независимо от рабочей частоты.

Daniel Kopylow

Перегрин

1.2 мкм LS-APD-ECL под 5 В потребляет меньше электроэнергии, чем 0.5 мкм CMOS под 3.3 В на частоте выше 780 МГц. В случае приложений с повышенным переключением транзисторов или с продвинутой биполярной технологией, переходная частота может быть далее понижена.

Daniel Kopylow

Перегрин

1.2 мкм LS-APD-ECL под 5 В потребляет существенно меньше электроэнергии, чем 0.8 мкм CMOS под 5 В, притом будучи существенно быстрее ECL.

Daniel Kopylow

Перегрин

Самая быстродействующая память в мире — LS-APD-ECL SRAM — может быть использована в качестве оперативной памяти в случае применения машинных кодов.

b-graf

Принцепс сената

Послезавтра - конец света

https://inosmi.ru/science/20200618/247621519.html

https://inosmi.ru/science/20200618/247621519.html

Антон Короленков

Проконсул

Послезавтра - конец света

https://inosmi.ru/science/20200618/247621519.html

Граждане, воздушная тревога,

граждане, спасайтесь ради бога

майки-трусики берите

и на кладбище бегите,

занимайте лучшие места.

Недавно интернет-пользователи были удивлены заметками о начале обратного отсчета до конца света, который якобы должен произойти 21 июня 2020 года.

Ну сёдня уже, слава Всевышнему, 22-е...

Michael

Принцепс сената

Красиво! В 1752 Британия перешла на григорианский календарь, убрав 11 дней. Значит, накопившаяся ошибка 11 дней * (2020-1752) = 2948 дней. Like. Забью в закладки.Послезавтра - конец света

https://inosmi.ru/science/20200618/247621519.html

Diletant

Великий Магистр

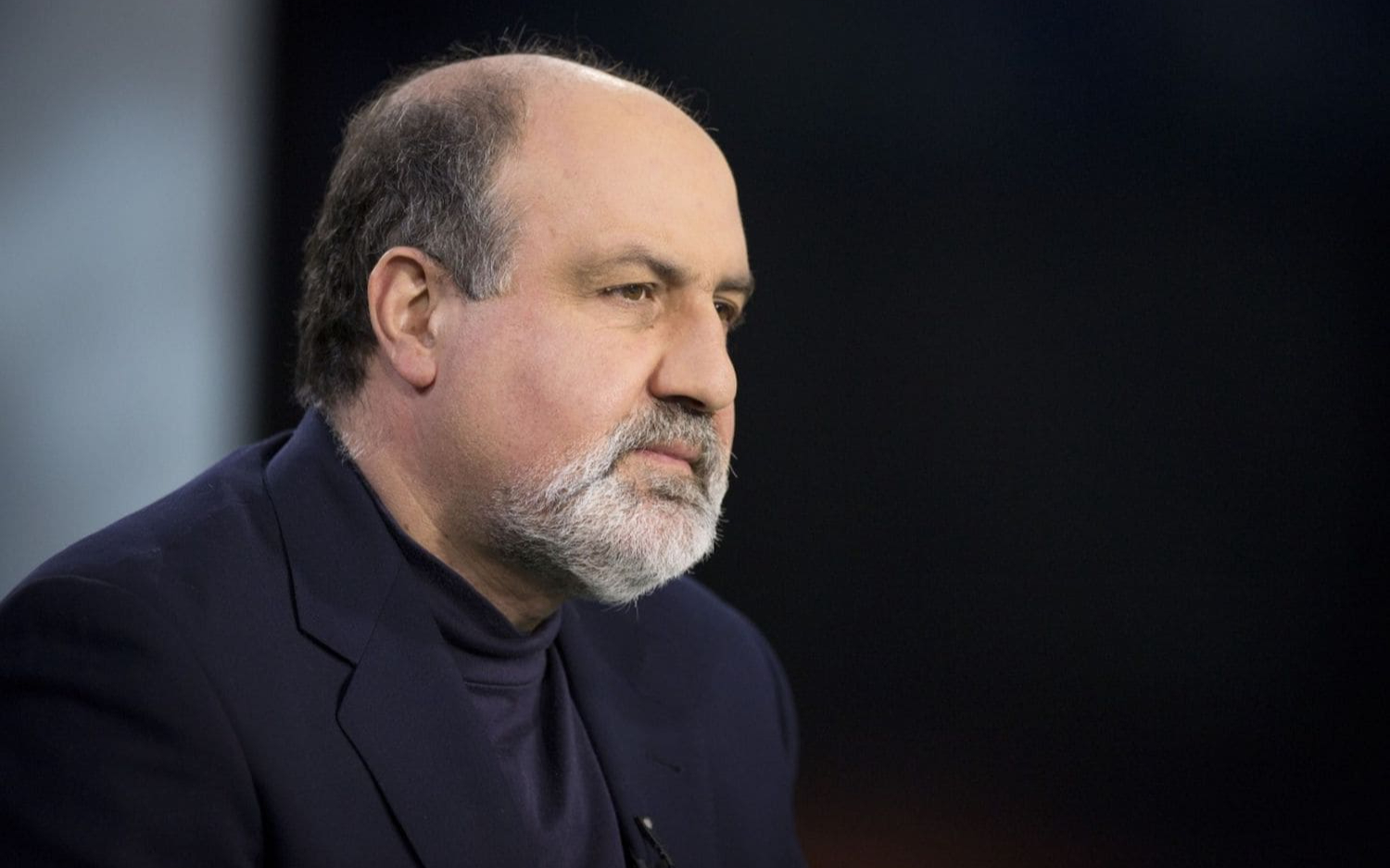

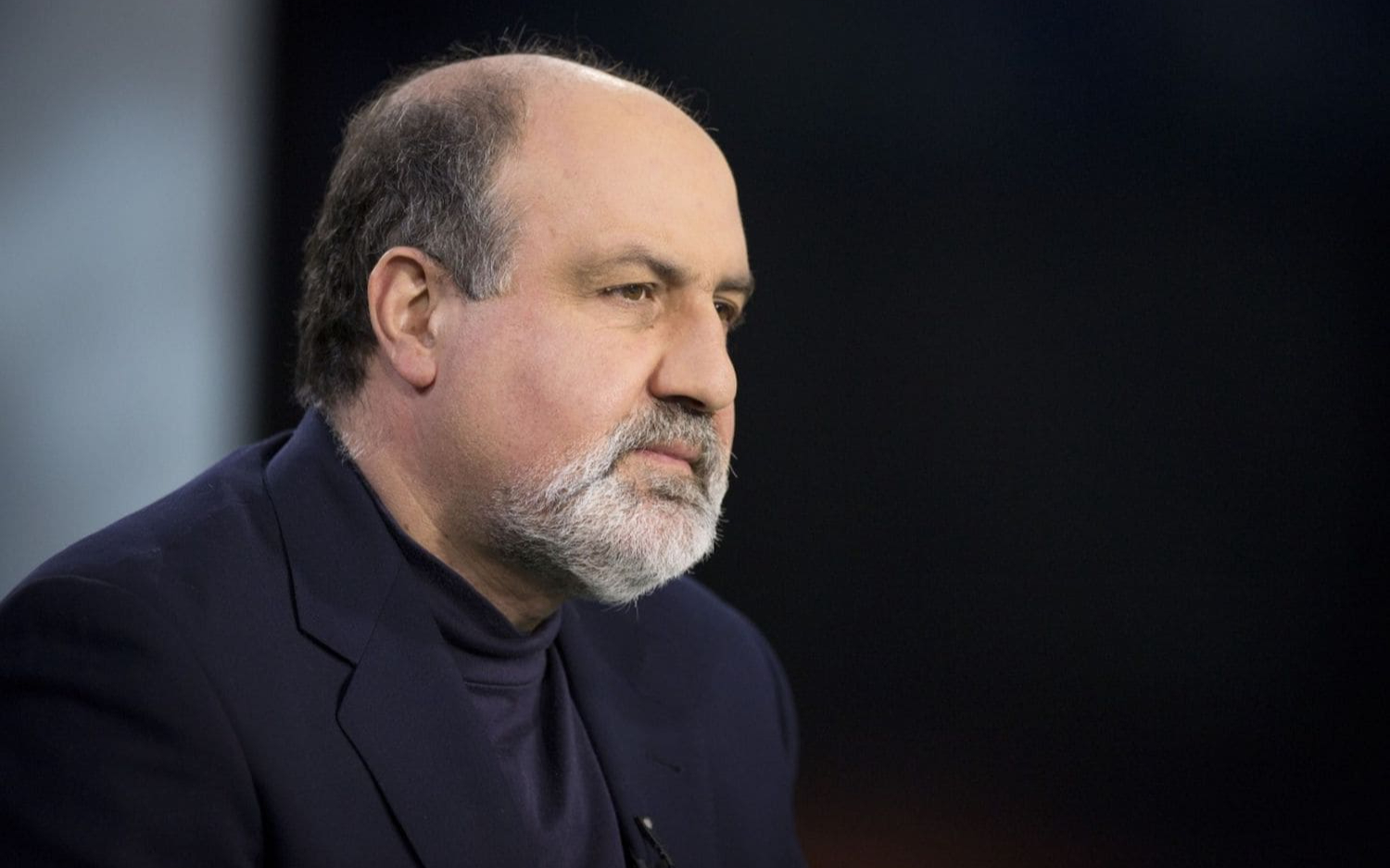

Порция прогностики Массима Талиба.

trends.rbc.ru

В т.ч. затронул недавно обсуждаемую тему гастрономической исключительности евреев...))) Бытие определяет сознание...

trends.rbc.ru

В т.ч. затронул недавно обсуждаемую тему гастрономической исключительности евреев...))) Бытие определяет сознание...

Пустые офисы и проблема госдолга: пять прогнозов Нассима Талеба | РБК Тренды

Какие предсказания бывшего трейдера сбылись, а в какие вмешались «черные лебеди»

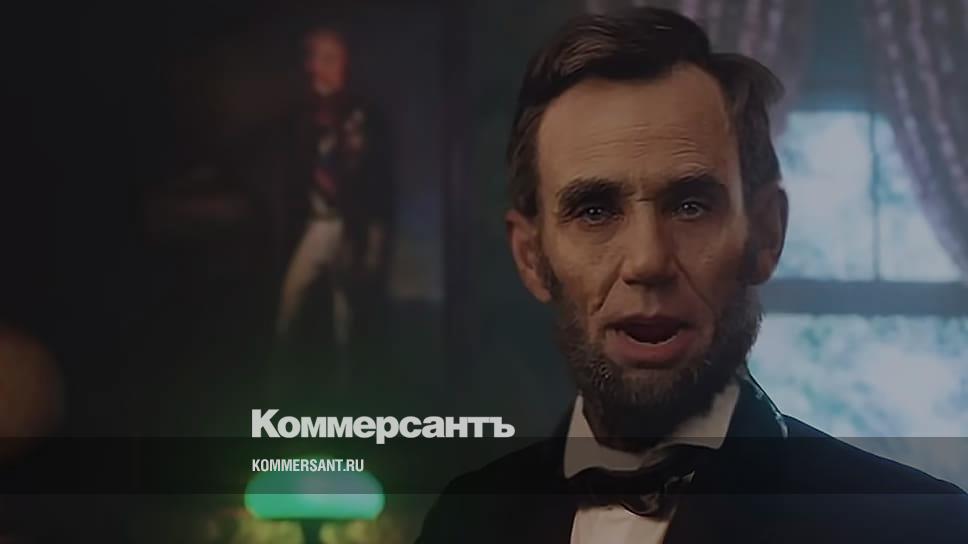

Виртуальное оживление мертвецов набирает обороты:

www.kommersant.ru

www.kommersant.ru

Сайт генеалогических исследований MyHeritage предложил пользователям новый сервис DeepNostalgia, позволяющий с помощью технологий ИИ «оживить» изображение на фото давно умерших родных. На анимированном изображении человек, которого уже нет на свете, улыбается, поворачивает голову, моргает и выглядит вполне живым. Спрос на новый сервис оказался настолько высоким, что уже в первые дни приложение несколько раз прекращало работу из-за перегрузки сайта.

ЖИИвее всех живых

Фотографии умерших «оживили» с помощью искусственного интеллекта

Поделиться: